- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

シリコンオンインシュレーターウェーハ

VeTek Semiconductor is a professional Chinese manufacturer of Silicon On Insulator Wafer, ALD Planetary Base, and TaC Coated Graphite Base. VeTek Semiconductor's Silicon On Insulator Wafer is an important semiconductor substrate material, and its excellent product characteristics make it play a key role in high-performance, low-power, high-integration and RF applications. We look forward to further cooperation with you.

お問い合わせを送信

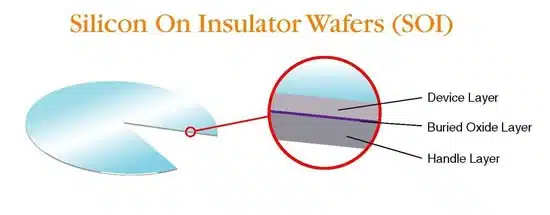

の動作原理ヴェテック・セミコンダクターのシリコンオンインシュレーターウェーハ主にそのユニークな構造と材料特性に依存します。そして SOIウェーハは 3 つの層で構成されます。最上層は単結晶シリコン デバイス層、中間は絶縁埋め込み酸化物 (BOX) 層、最下層は支持シリコン基板です。

シリコン・オン・インシュレーター・ウェーハ (SOI) の構造

絶縁層の形成: Silicon On Insulator Wafer は通常、Smart Cut™ 技術または SIMOX (Separation by IMplanted OXygen) 技術を使用して製造されます。 Smart Cut™ テクノロジーは、水素イオンをシリコンウェーハに注入して気泡層を形成し、水素が注入されたウェーハを支持シリコンに接着します。ウエハース。

![]()

熱処理後、水素が注入されたウェーハはバブル層から分離され、SOI 構造が形成されます。SIMOXテクノロジー高エネルギーの酸素イオンをシリコンウェーハに注入して、高温で酸化シリコン層を形成します。

寄生容量を低減する:のBOX層炭化ケイ素ウェハデバイス層とベースシリコンを効果的に分離し、コストを大幅に削減します。g 寄生容量。この絶縁により消費電力が削減され、デバイスの速度とパフォーマンスが向上します。

ラッチアップ効果を回避する: の n ウェルおよび p ウェルデバイスSOIウェーハは完全に分離されており、従来の CMOS 構造におけるラッチアップ効果を回避します。これにより、ウェーハSOI より高速に製造できるようになります。

エッチストップ機能: の単結晶シリコンデバイス層SOIウェーハのBOX層構造はMEMSや光電子デバイスの製造を容易にし、優れたエッチストップ機能を提供します。

こうした特徴を通じて、シリコンオンインシュレーターウェーハ半導体プロセスにおいて重要な役割を果たし、集積回路 (IC) と微小電気機械システム (MEMS)産業。皆様との更なるコミュニケーションとご協力を心よりお待ちしております。

200mm SOl ウェーハの仕様パラメータ:

|

200 mm SOl ウェーハ仕様 |

||

|

いいえ |

説明 |

価値 |

| デバイスシリコン層 | ||

| 1.1 |

厚さ |

220nm +/-10nm |

| 1.2 |

製造方法 |

チェコ共和国 |

| 1.3 |

結晶方位 |

<100> |

| 1.4 | 導電性の種類 | p |

| 1.5 | ドーパント |

ボロン |

| 1.6 |

平均抵抗率 |

8.5 - 11.5 0hm*cm |

| 1.7 |

RMS (2x2μm) |

<0.2 |

| 1.8 |

LPD (サイズ>0.2um) |

<75 |

| 1.9 |

0.8ミクロン(面積)を超える大きな欠陥 |

<25 |

| 1.10 |

エッジ欠け、キズ、クラック、ディンプル/ピット、ヘイズ、オレンジピール(目視検査) |

0 |

| 1.11 |

結合ボイド: 目視検査 > 直径 0.5mm |

0 |

Silicon On Insulator ウェーハの製造ショップ: