- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

チップ製造:MOSFETのプロセスフロー

2024-07-31

チップの製造プロセスにはフォトリソグラフィー、エッチング, 拡散、薄膜、イオン注入、化学機械研磨、洗浄など。この記事では、これらのプロセスがどのように順番に統合されてMOSFETが製造されるのかを大まかに説明します。

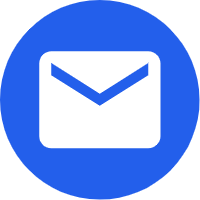

1.まず、基板シリコン純度は最大 99.9999999% です。

![]()

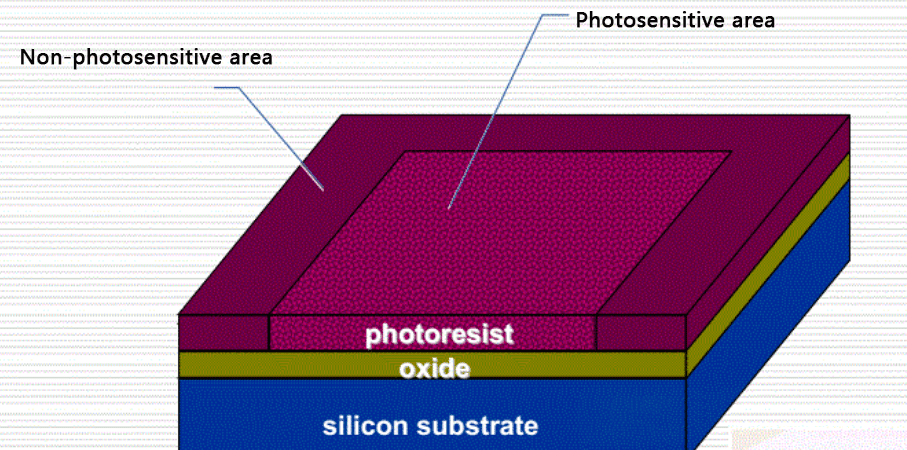

2. シリコン結晶基板上に酸化膜を成長させます。

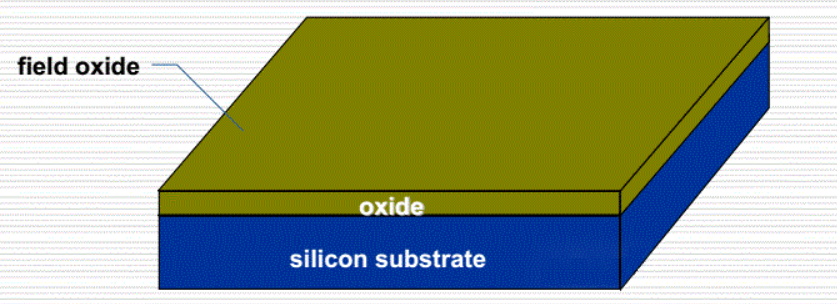

3. フォトレジストを均一にスピンコートします。

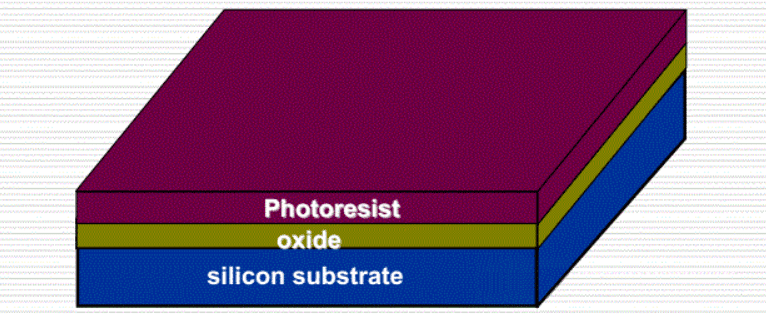

4.フォトマスクを介してフォトリソグラフィーを実行し、フォトマスク上のパターンをフォトレジストに転写します。

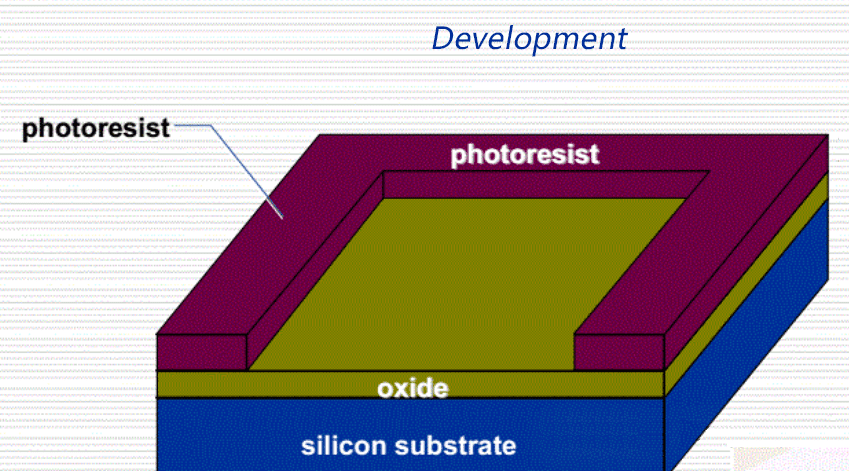

5. 現像後、感光領域のフォトレジストが洗い流されます。

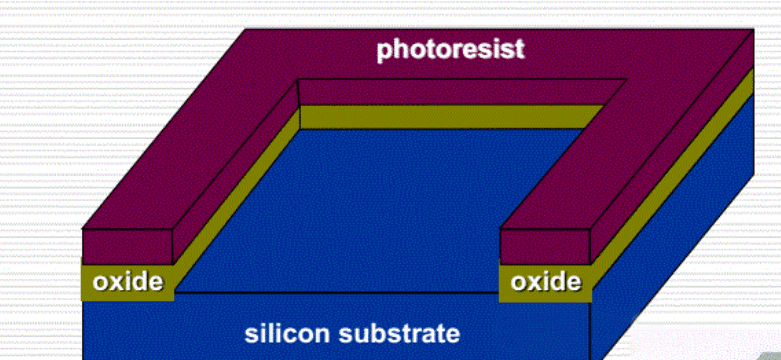

6. フォトレジストで覆われていない酸化膜をエッチングにより除去し、フォトリソグラフィーのパターンを転写します。ウエハース.

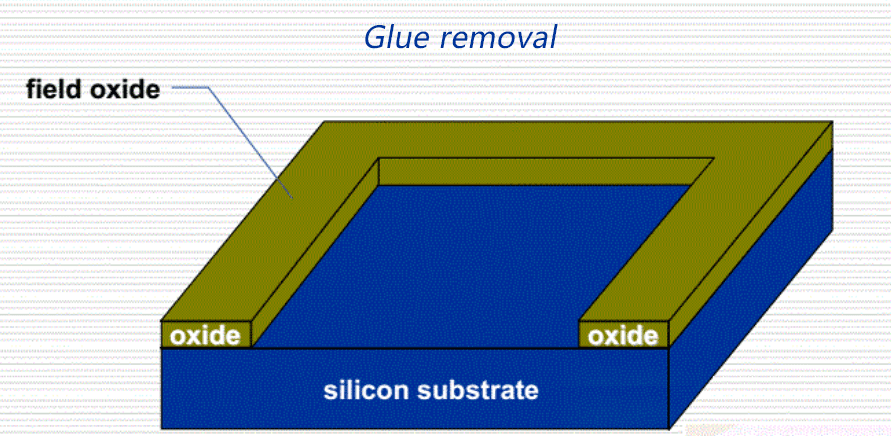

7. 余分なフォトレジストを洗浄して除去します。

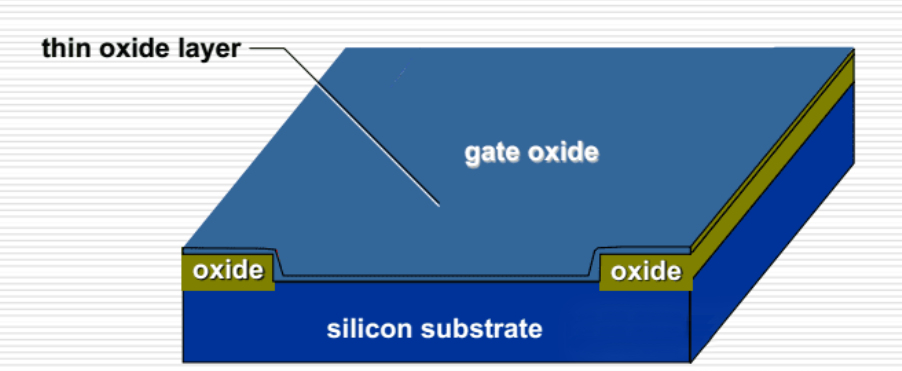

8. 別のシンナーを塗布します酸化皮膜。その後、上記のフォトリソグラフィーとエッチングにより、ゲート領域の酸化膜のみが残る。

9. その上にポリシリコンの層を成長させます

![]()

10. ステップ 7 と同様に、フォトリソグラフィーとエッチングを使用して、ゲート酸化層上にポリシリコンのみを残します。

![]()

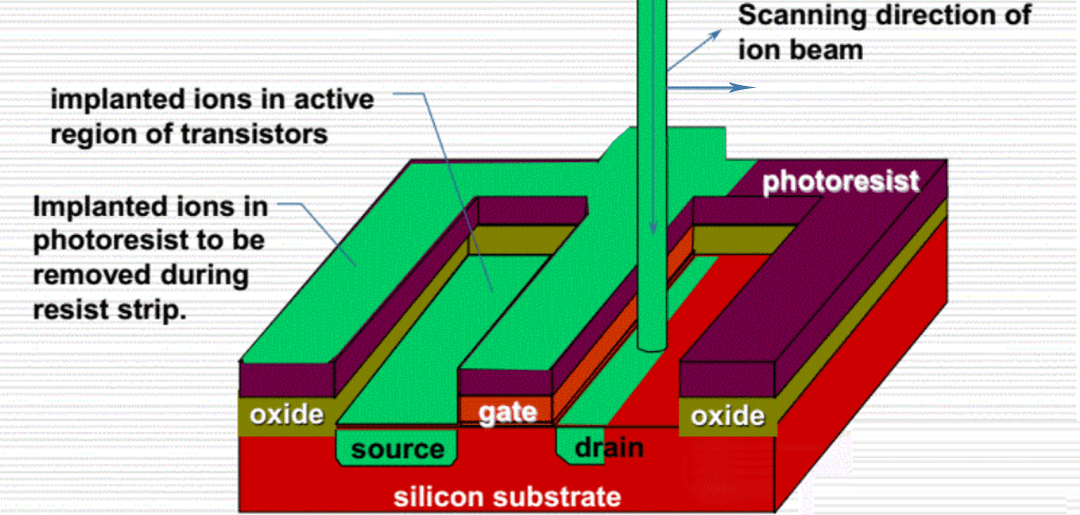

11.フォトリソグラフィー洗浄によって酸化層とゲートを覆い、ウェーハ全体がきれいになるようにします。イオン注入済み、ソースとドレインがあります。

![]()

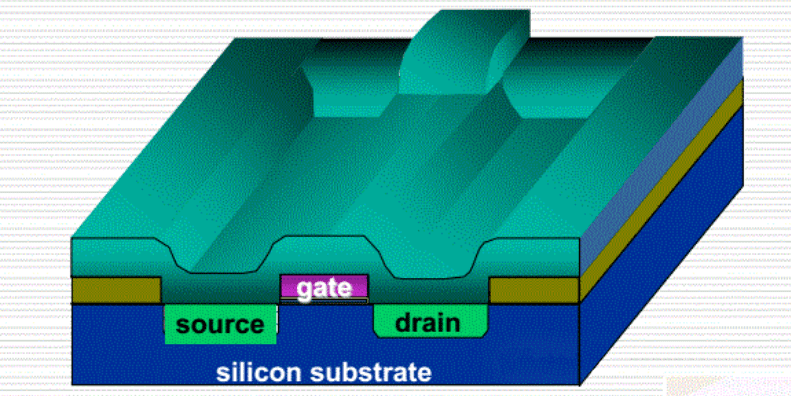

12. ウェーハ上に絶縁膜の層を成長させます。

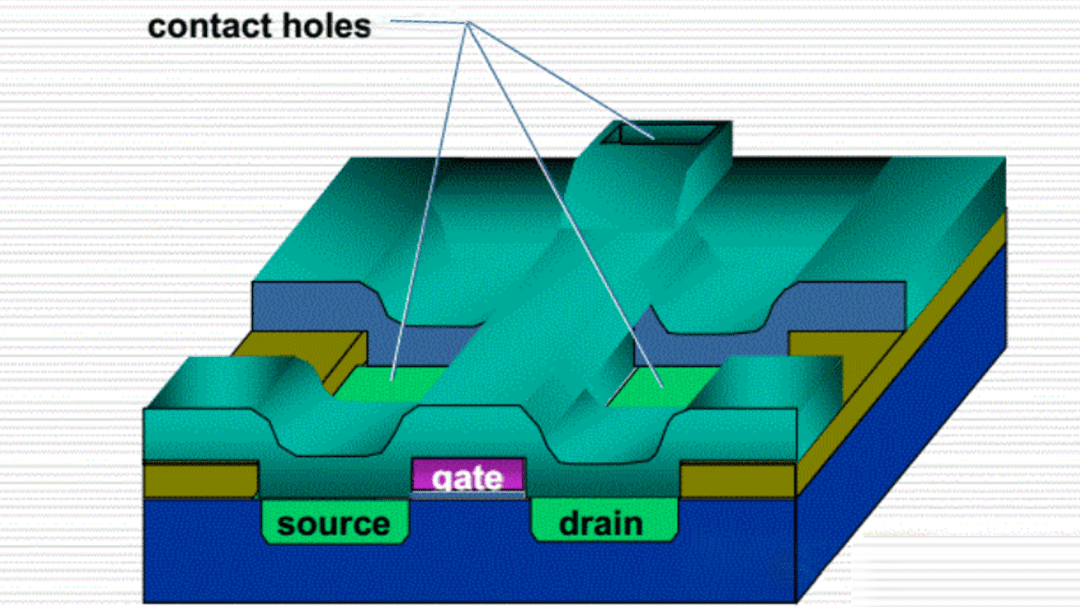

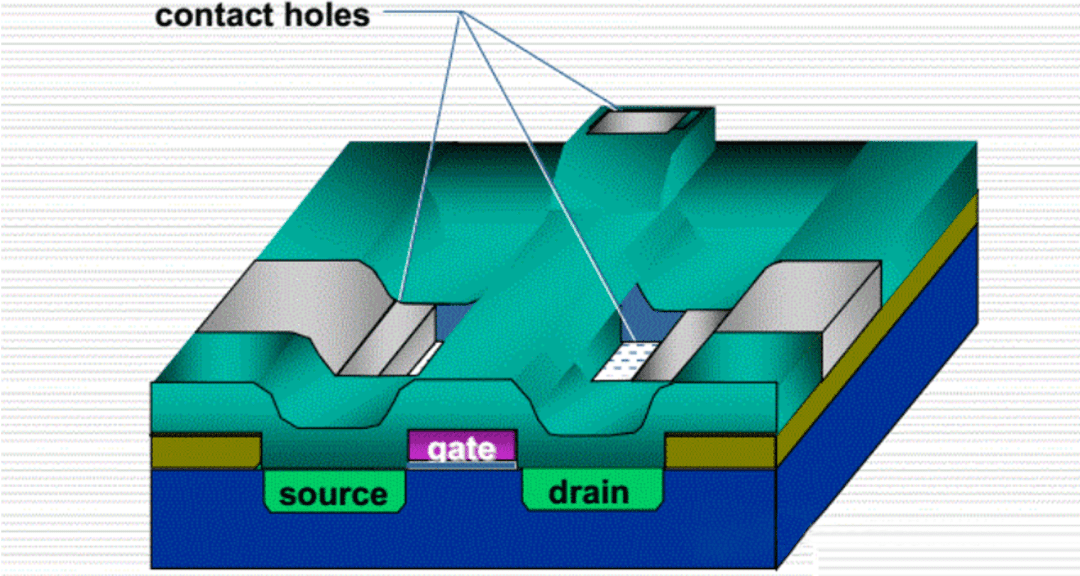

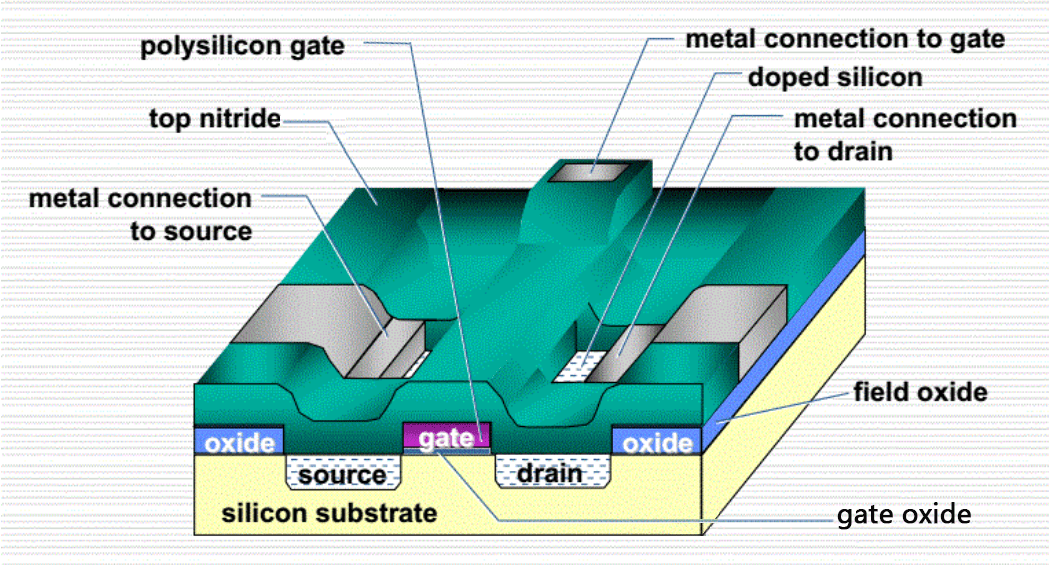

13. フォトリソグラフィーとエッチングにより、ソース、ゲート、ドレインのコンタクトホールをエッチングします。

14. 次に、ソース、ゲート、ドレイン用の導電性金属ワイヤができるように、エッチングされた領域に金属を堆積します。

最終的に、さまざまなプロセスを組み合わせて完全な MOSFET が製造されます。

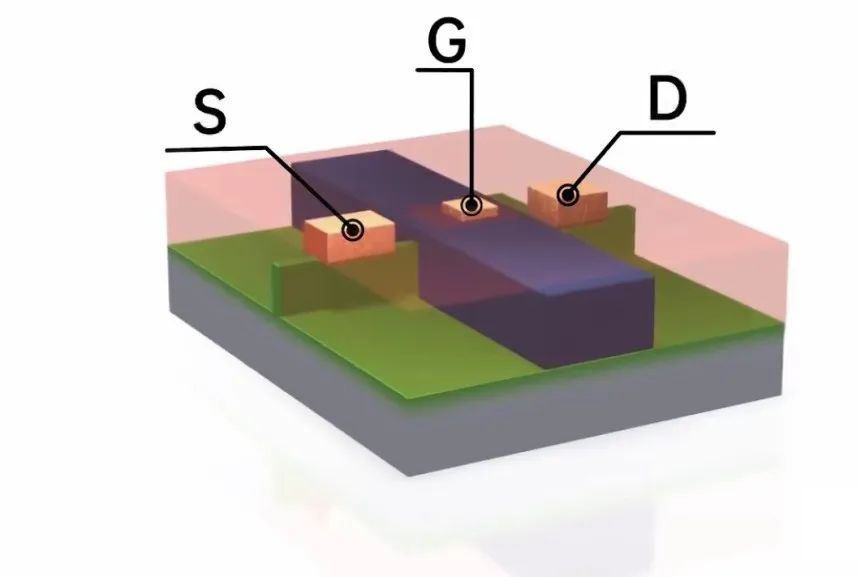

実際、チップの最下層は多数のトランジスタで構成されています。

MOSFETの製造図、ソース、ゲート、ドレイン

![]()

さまざまなトランジスタが論理ゲートを形成する

![]()

論理ゲートは演算ユニットを形成します

![]()

最終的には爪ほどの大きさのチップになります

![]()